ChipFlow

@chipflow_io

Helping product companies to make their own chips

ID: 1446077195395420161

https://chipflow.io 07-10-2021 11:37:47

40 Tweet

264 Takipçi

7 Takip Edilen

This week Matthew Venn of the Zero To ASIC Course returns to The Amp Hour to talk about what has been happening in the world of #OpenSource #Silicon, both the tools that make things go and the projects that people are creating. buff.ly/3R2nLGN

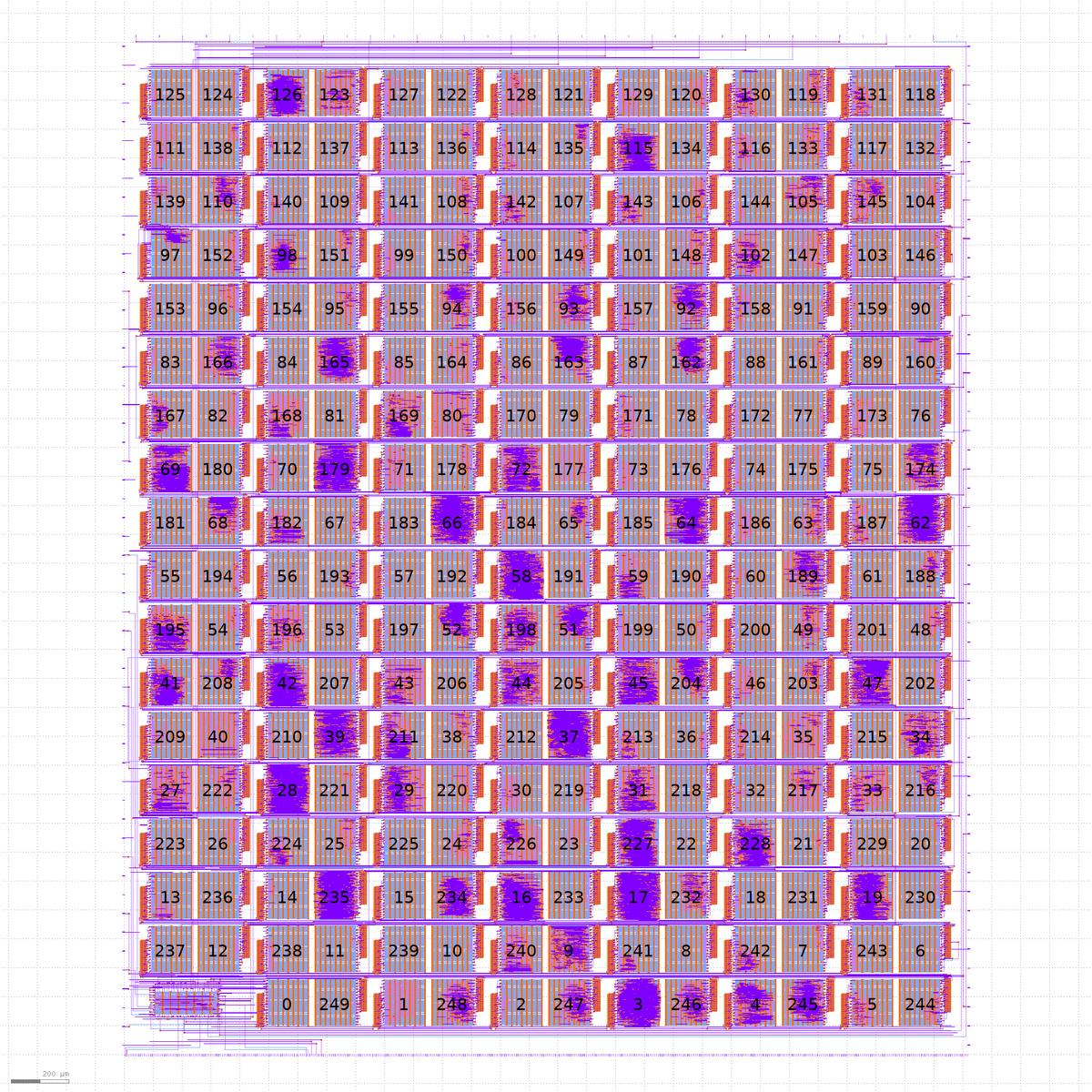

And thanks to Matthew Venn for helping me prepare some of the content! Have a look at his Zero to ASIC course and the Tiny Tapeout project if you are looking for a guided way into the world of ASIC development.

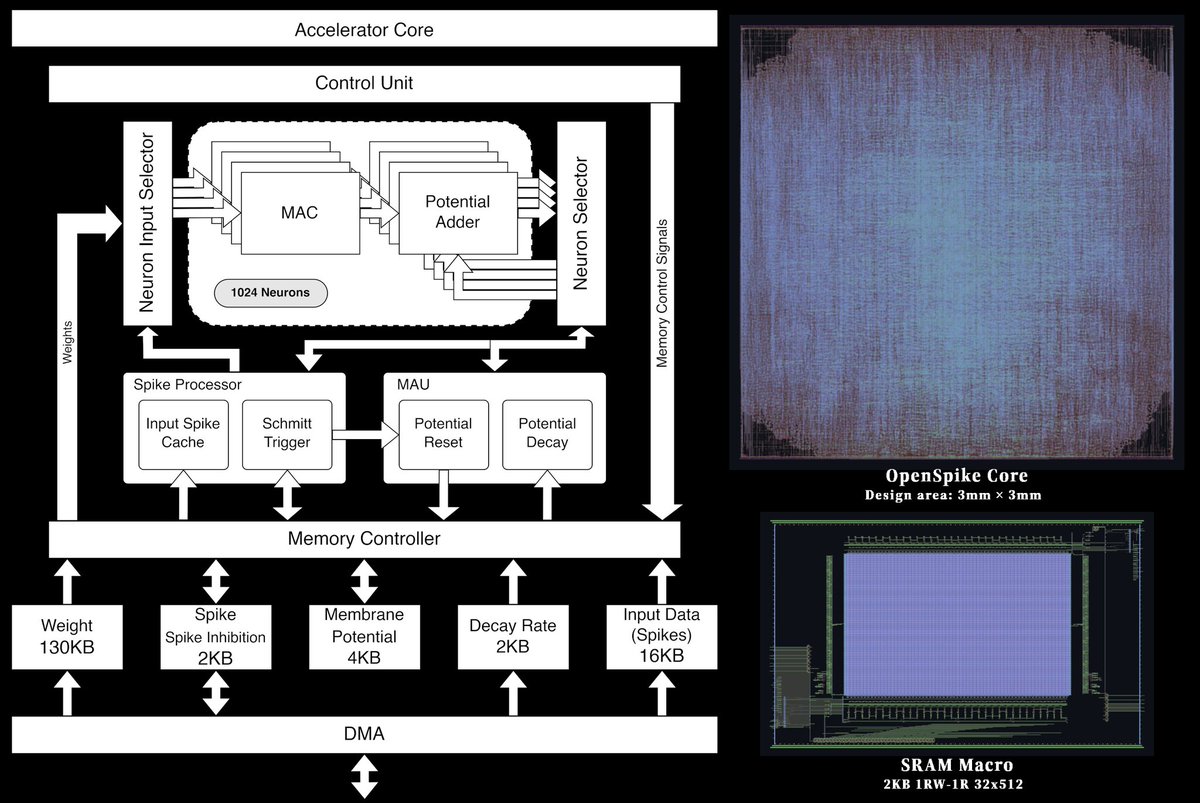

My first ever paper was accepted to ISCAS 2023. It's a fully opensource neuromorphic chip. Download the paper: arxiv.org/abs/2302.01015 Checkout the repository: github.com/sfmth/OpenSpike Special thanks to @mguthaus and Jason Eshraghian, co-authors of this work.

New guest post by Victor Suarez Rovere and PipelineC (fosstodon.org/@pipelinec)! In this article we present a tool flow that takes C++ code describing a raytraced game, and produces digital logic that can be implemented in off-the-shelf #FPGA with no hard or soft CPU used. blog.yosyshq.com/p/3d-raytracin…

It's Valentine's day, so let's bring some love to you all with a new edition of El Correo Libre fossi-foundation.org/ecl/ecl59 This time we have the new FOSSi toolchain from QuickLogic Corp., Hossein Askari's NNA called BARVINN, Antmicro's NVMe ML accelerator and much more. Enjoy!

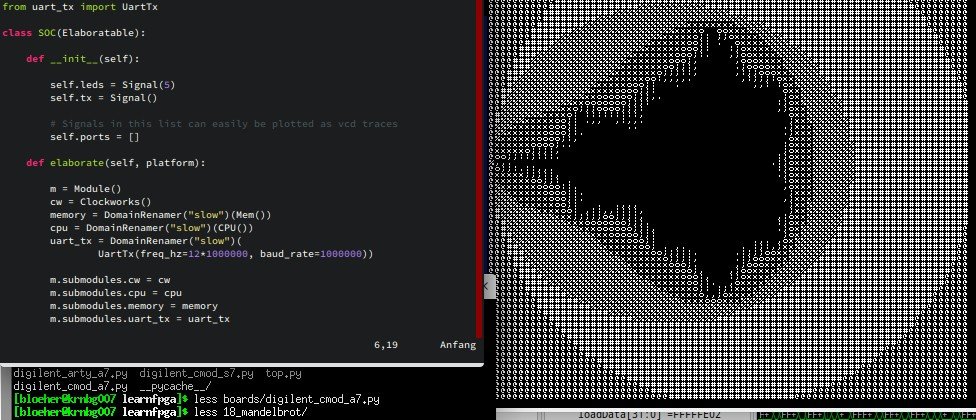

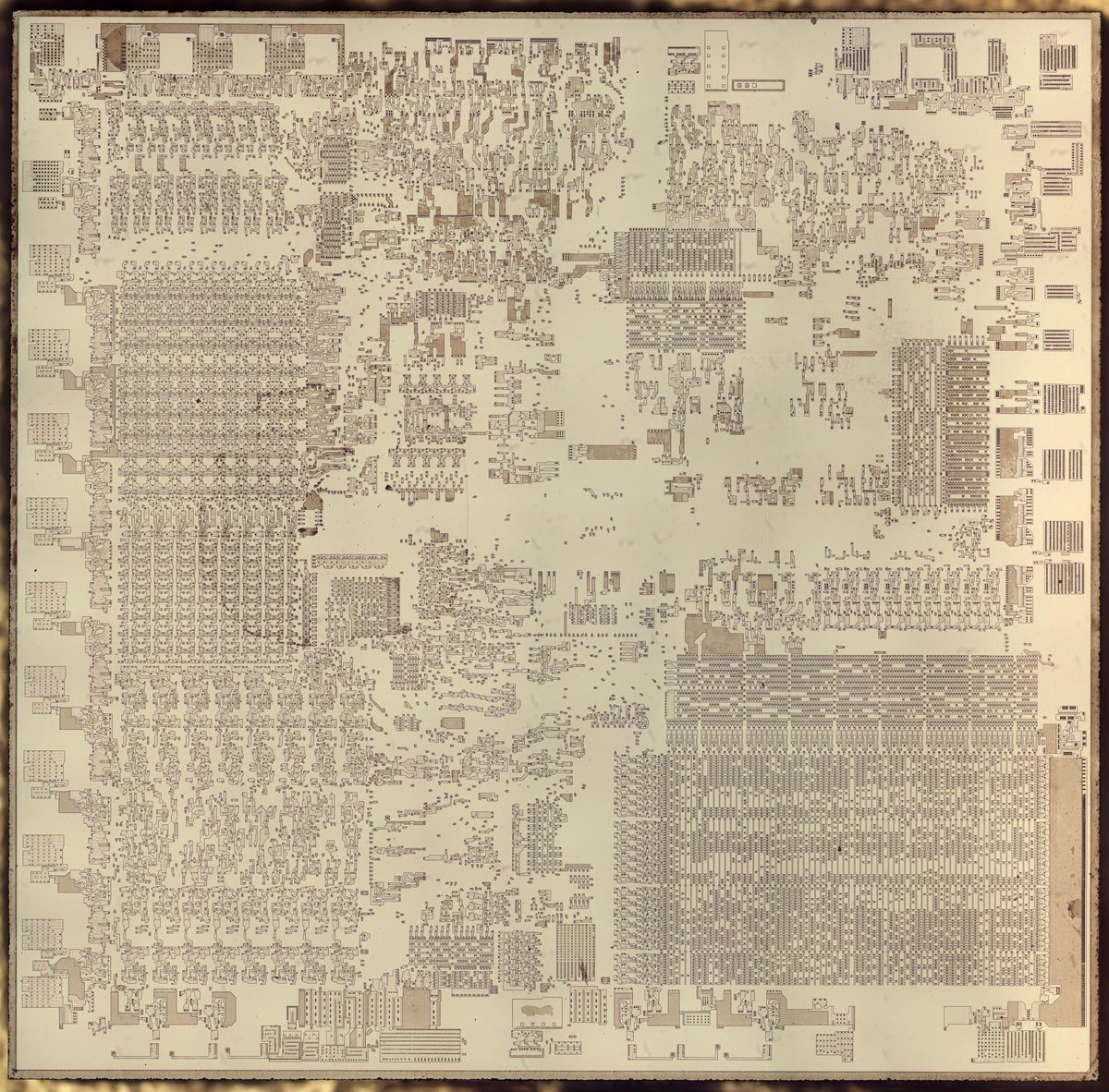

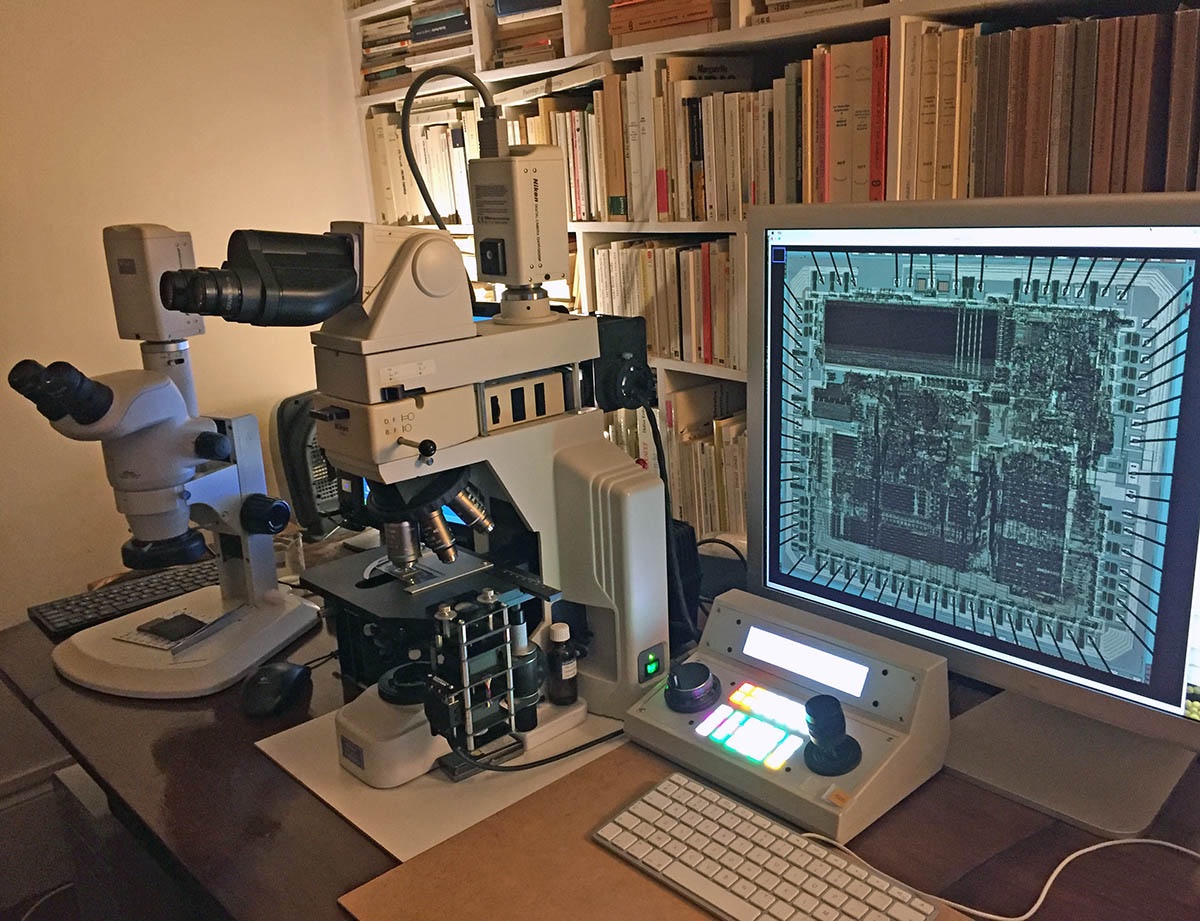

In this great post by bastian, bl0x we follow his journey of implementing a #RISCV CPU with Amaranth #HDL. Some great background on using #FPGAs for science, and his challenges and successes while following Bruno Levy 's excellent Blinker to RISCV guide. blog.yosyshq.com/p/blinker-to-r…