Epsilon

@2lysens

Hacker, surfer, engineer, retro-computer enthusiast

ID: 1445386367224238085

https://github.com/epsilon537 05-10-2021 13:52:44

31 Tweet

80 Takipçi

76 Takip Edilen

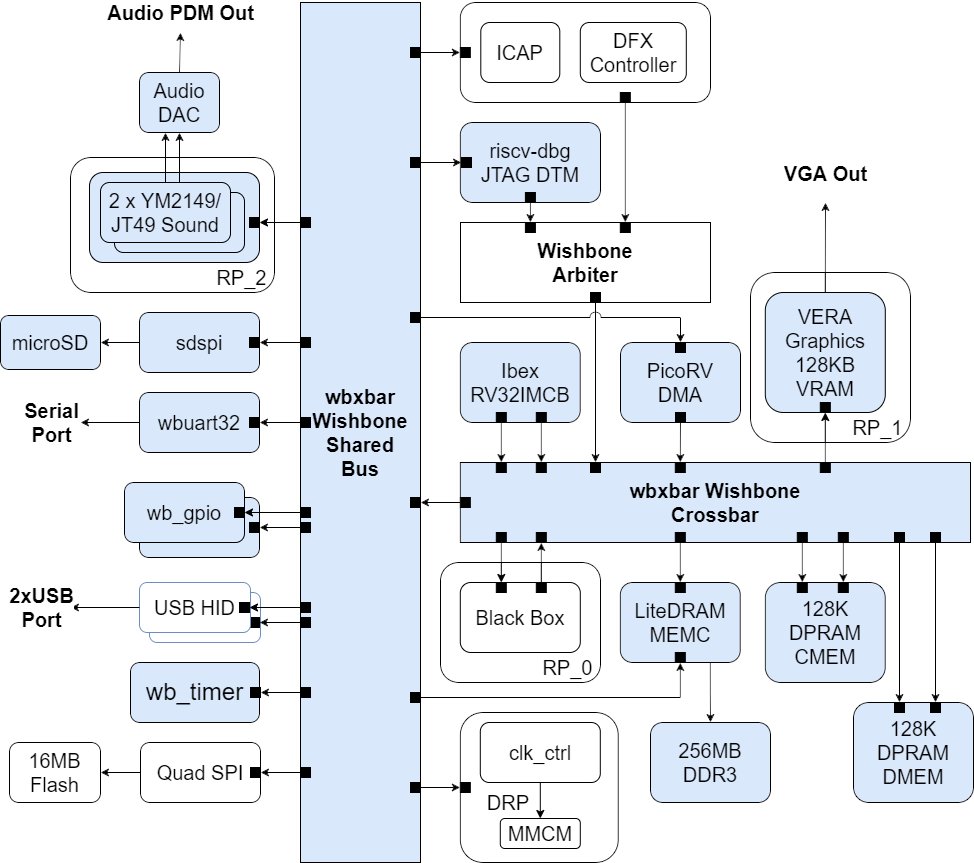

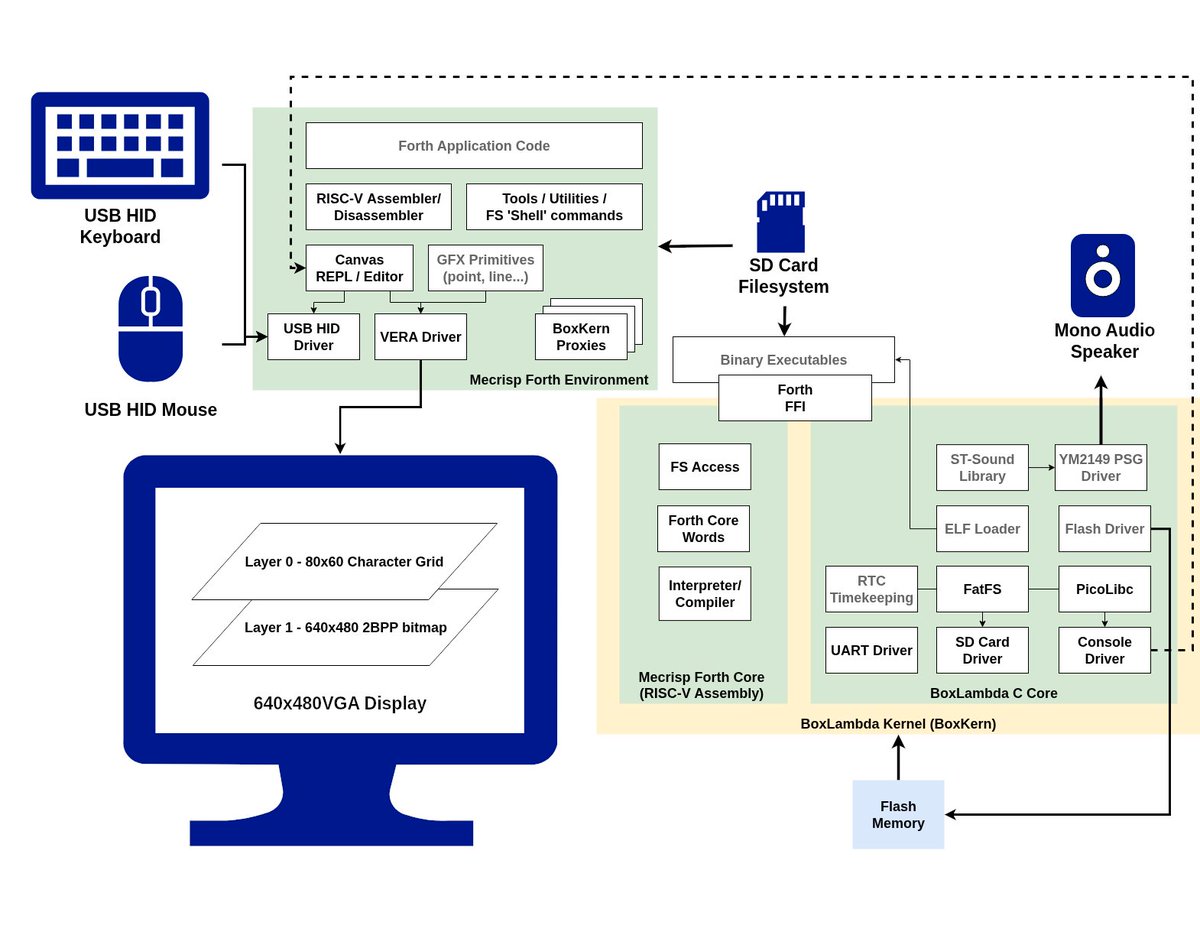

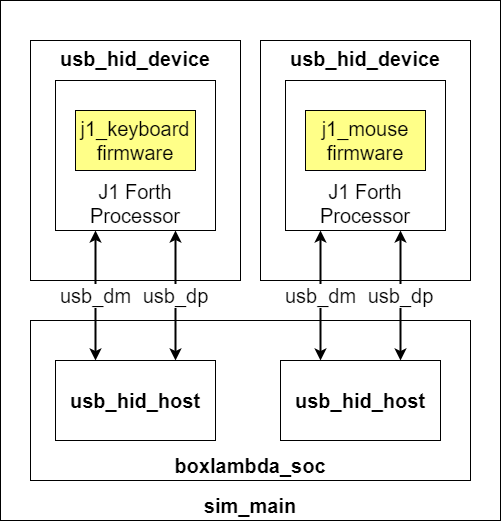

BoxLambda Devlog: On USB HID, Keyboard LEDs, and device emulation. epsilon537.github.io/boxlambda/usb-… nand2mario Machdyne UG #FPGA #USB #RISCV #FORTH #j1

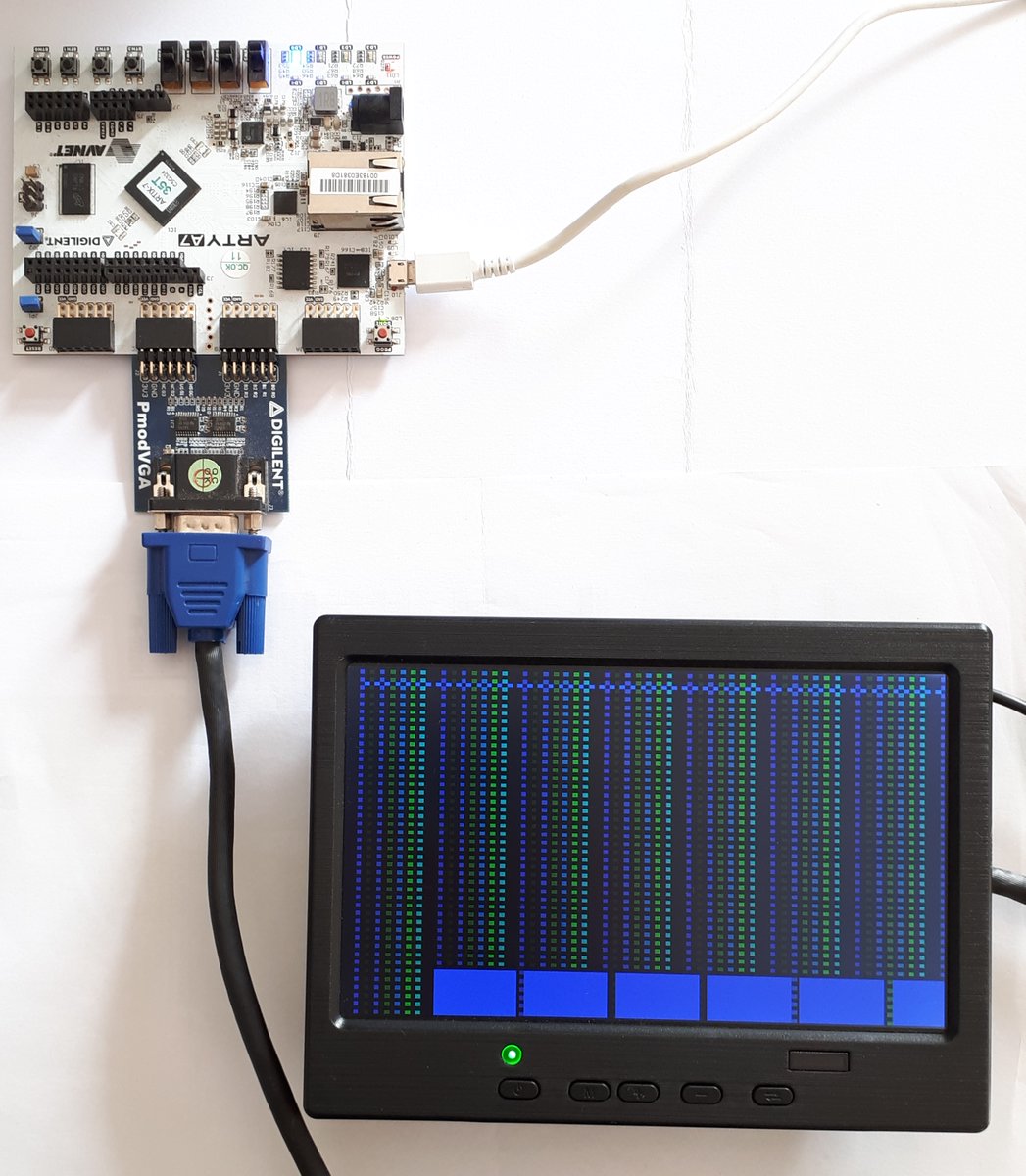

I just pushed a new BoxLambda release. The main additions are: - the BootLoader: boxlambda.readthedocs.io/en/latest/sw_c… - a complete Register Map: boxlambda.readthedocs.io/en/latest/regi… For a complete list of changes, please refer to the Release Notes: github.com/epsilon537/box… #FPGA #RISCV