PULP Platform

@pulp_platform

A joint effort of @ETH_en, University of Bologna @Unibo + partners for Parallel Ultra-Low Power computing. Boldly designing open hardware since '13.

ID: 703176595742150660

http://pulp-platform.org 26-02-2016 11:15:39

3,3K Tweet

6,6K Takipçi

1,1K Takip Edilen

More from Charlie The Bear at the #RISCV Summit EU in Paris 😀. Below our guys Victor Victor Jung , Sergio Sergio Mazzola who together with Charlie The Bear welcome the new #RISCV CEO Andrea Gallo.

Sergio's Sergio Mazzola #RISCV Summit EU presentation on "MemPool Flavors: Between Versatility and Specialization in a RISC-V Manycore Cluster" is now online, as well: pulp-platform.org/docs/riscvsumm…

Our #HotChips2025 poster submission was just accepted. Check out now the two-page abstract on "Basilisk: A 34 mm² End-to-End Open-Source 64-bit Linux-Capable RISC-V SoC in 130nm BiCMOS" on arXiv: arxiv.org/pdf/2505.10060 Thomas Benz

Victor's poster Victor Jung "Fused-Tiled Layers: Minimizing Data Movement on RISC-V SoCs" presented at #RISCV Summit Europe in Paris is now on our website: pulp-platform.org/docs/riscvsumm…

We had a great week in #Paris at the RISC-V International. Very productive talks with PULP Platform and nice exchange with Axelera AI about extensions for wireless communication. #Satellites and #submarines were also part of this week European Space Agency NASA Many thanks to Research in Germany - Initiative of the BMBF #France #risc

And here is the poster "On-Device Federated Continual Learning on RISC-V-based Ultra-Low-Power SoC for Intelligent Nano-Drone Swarms" by Lars and Cristian Cristi Cioflan presented at the #RISCV Summit Europe in Paris: pulp-platform.org/docs/riscvsumm… & arxiv.org/abs/2503.17436

14 team members, 2640 m altitude difference, 114 km in 9h37min. We ranked 287th at the 50th edition of the SOLA Stafette. Congrats Christoph Leitner Cristi Cioflan Giusy Spacone Victor J. Kartsch Marco Bertuletti Þórir Már 🇺🇦 Victor Jung corporate.migros.ch/de/verantwortu… sportrait.com/overview/event…

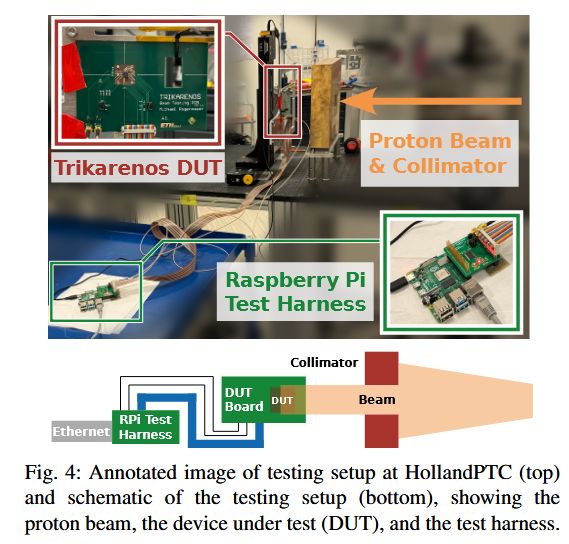

Our paper Michael Rogenmoser "Trikarenos: Design and Experimental Characterization of a Fault-Tolerant 28nm RISC-V-based SoC" accepted as IEEE TNS paper now contains comparison of the radiation results with fault injection simulations in the netlist. See arxiv.org/pdf/2407.05938

"How to keep pushing ML accelerator performance? Know your rooflines!" Check out the survey of key trends for more efficient ML accelerators by Marian Verhelst, Luca Benini Luca Benini and Naveen Verma: arxiv.org/pdf/2505.16346

"Navigate Your Way to a Career in Semiconductors" event for students recently took place at ETH Zurich. Organized by EFCL and Cristina Borelli, below Andrea Cossettini and guests Jang Taekwang, Laura Bégon-Lours & for industry Chiara Martelli & Richa Bubna designthesolution.org/event/navigate…