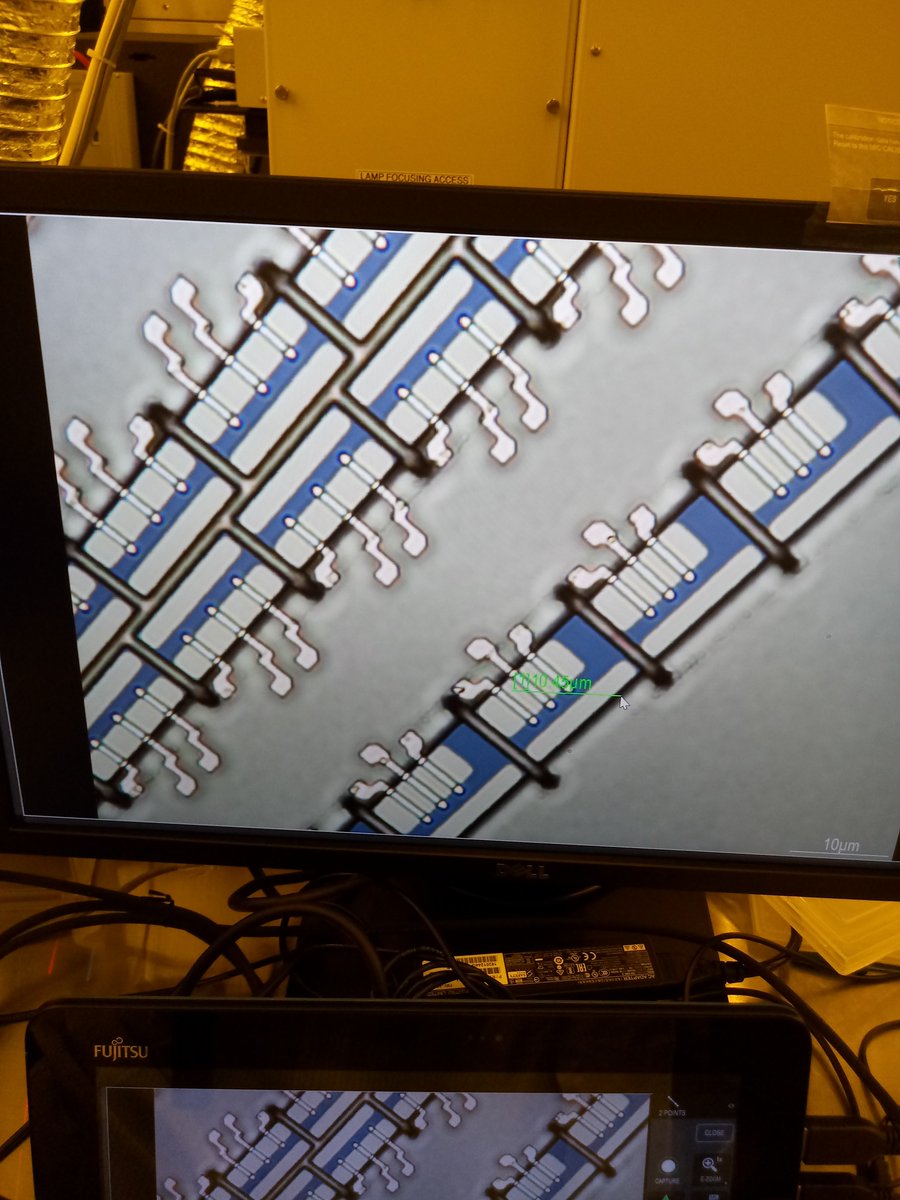

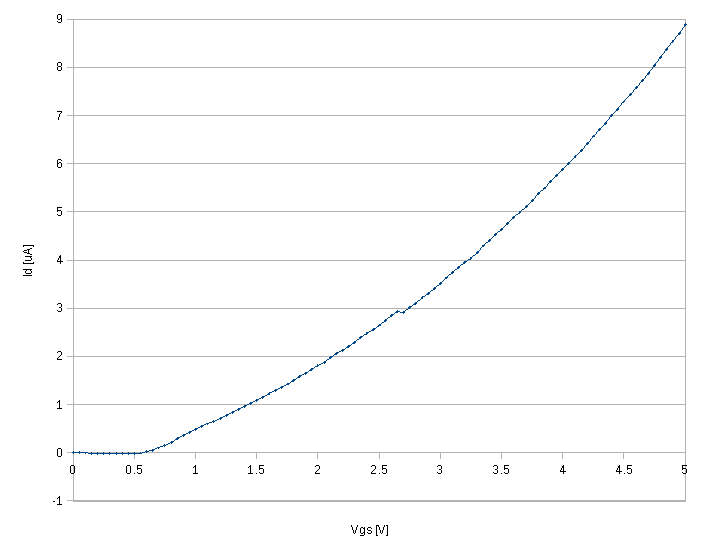

LibreSilicon

@libresilicon

The official Twitter account of the LibreSilicon team, keeping you up to date with the most recent developments in the project.

ID: 1079736393906245633

http://libresilicon.com 31-12-2018 13:49:51

31 Tweet

305 Takipçi

0 Takip Edilen