Arduissimo

@arduissimo

RISC-V 32-Bit project. System Hyper Pipelining, Dynamic Multithreading, Wave-Pipelining, MultiCore Arduino on FPGA and ASIC, Virtual Peripherals.

ID: 387292711

http://cloudx.cc 08-10-2011 20:02:48

660 Tweet

2,2K Takipçi

1,1K Takip Edilen

As the #ISSCC23 program is out, it's my pleasure to announce our work on #Marsellus will be in the Heterogeneous ML Accelerator session! It is a PULP Platform SoC with 16 #riscv cores and a flexible DNN accel for 12.4TOPS/W@136 GOPS AI. Davide Rossi Gianna Paulin Luca Benini

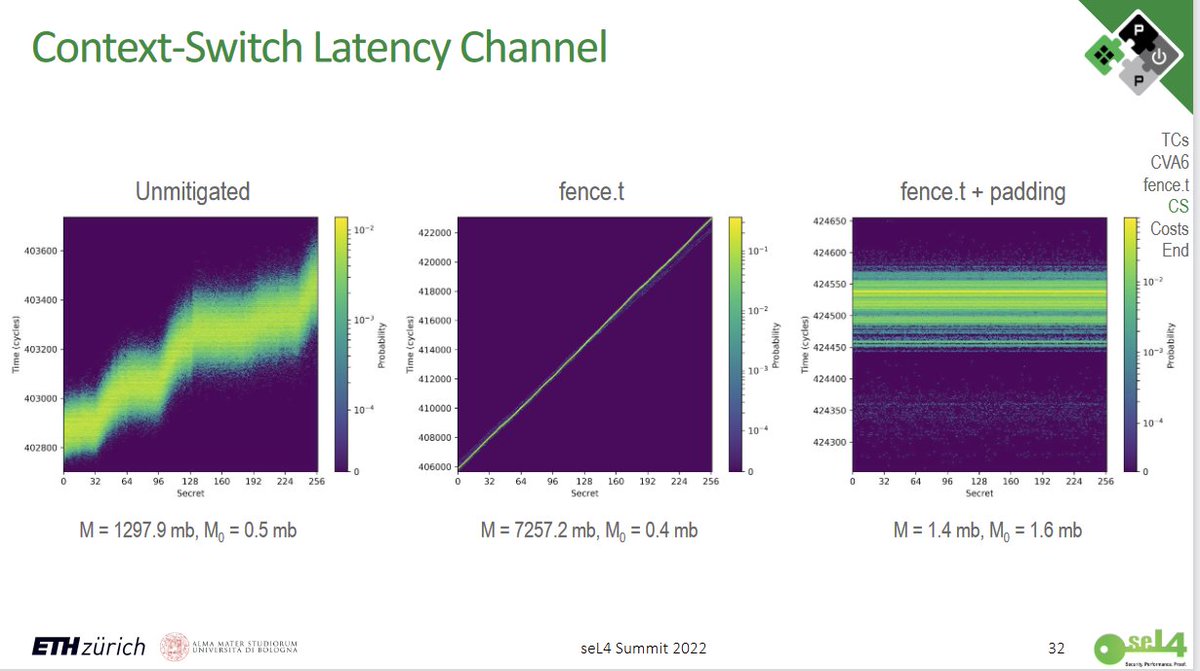

Would you like to learn more about fence.t instruction? Nils's Nils Wistoff slides from sel4 Summit presenting this novel RISC-V instruction that clears the processor's microarchitectural state are now online as well: sel4.systems/Foundation/Sum…