Andrew Elbert Wilson

@fpga_zealot

ID: 751503987380105216

https://discord.gg/k9BYa9VrR3 08-07-2016 19:51:27

708 Tweet

1,1K Takipçi

395 Takip Edilen

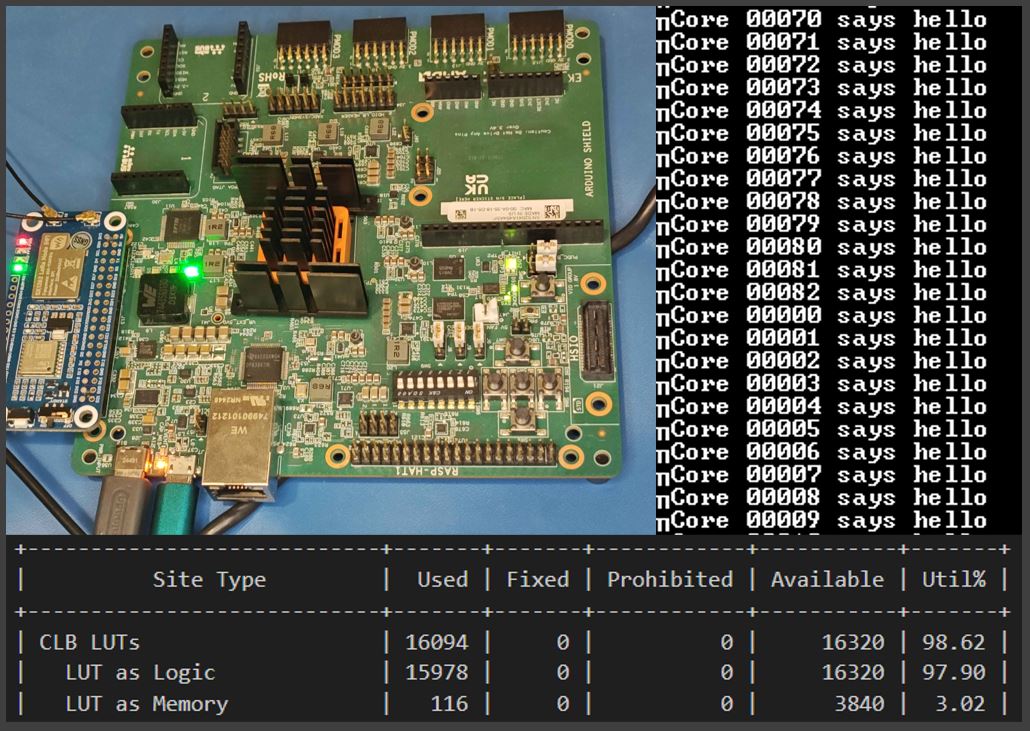

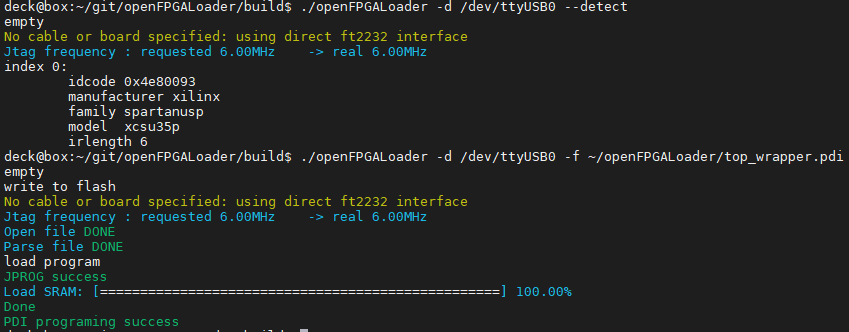

Here is the CoreScore for AMD’s Spartan UltraScale+ on the SCU35 dev board ⇒ 83 SERV RISC-V cores! Awesome, easy-to-use benchmark from Olof Kindgren . I’ll have the basic PR up soon.