Angelo Garofalo

@ang__93

ID: 346061150

31-07-2011 17:17:35

34 Tweet

56 Followers

209 Following

Our congratulations to Angelo Angelo Garofalo who just won the ISSCC 2023 Outstanding Forum Presenter Award for his last year's contribution "Is an AI Accelerator All You Need?". Check out the talk pulp-platform.org/docs/isscc2023…

Opportunity for paper submission at the Safety and Security in Heterogeneous Open System-on-Chip Platforms Workshop All the details here: ssh-soc-workshop.github.io/2024/ #opensource #riscv #security #safety #heterogeneous #soc @openhwgroup PULP Platform EPFL Ecocloud

Nice opportunity to submit a paper! Luca Benini, Davide Rossi & Angelo Garofalo are organizing SSH-SoC collocated with #DAC2024. Jonathan Balkind, John East, Jon Michelson zeroRISC, Jose Martins #UMinho & Rafail Psiakis Technology Innovation Institute among invited speakers. Learn more: ssh-soc-workshop.github.io/2024/.

OSHW24 collocated with CF'24 takes place next week. We will be there with Gigabit, DMA-enhanced Open-Source Ethernet Controller for Mixed-Criticality Systems Chaoqun Liang & NARS: Neuromorphic Acceleration through Register-Streaming Extensions on RISC-V Cores computingfrontiers.org/2024/program.h…

The second Open-Source Hardware Workshop at #CF24 has just finished in Italy, what an great event!! Our Davide Schiavone was co-charing the event with ETH Zürich PULP Platform and Uni Bologna and Poly Torino. Great talks also including our #OpenHW #CVA6 🤩 #semiconductor #opensource

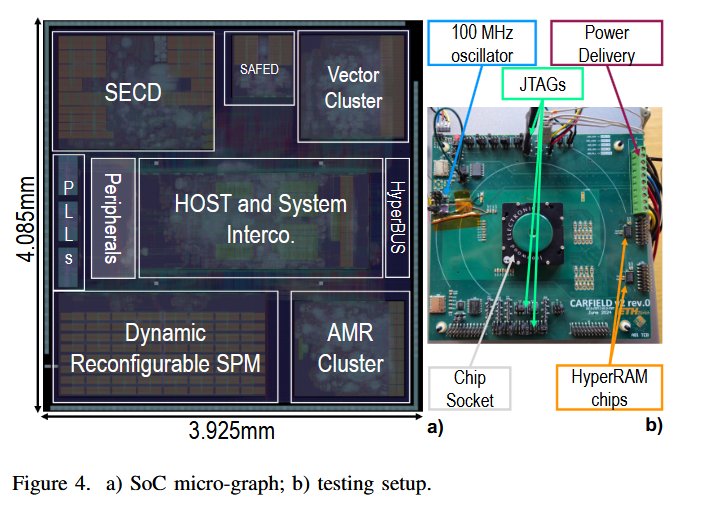

Tadaa! Carfield has just printed its first hello world string. Thanks to DUTCTL presented at #RISCV summit and the amazing work on standardizing Cheshire, we could bring Carfield up in less than 4 hours! pulp-platform.org/docs/riscvmuni… asic.ethz.ch/2023/Carfield.… Thomas Benz

We have recently taped out ASTRAL, a flexible, high-performance, secure & reliable heterogeneous SoC based on PULP, targeting space applications🚀. Learn more: asic.ethz.ch/2024/Astral.ht… #RISCV Yvan Tortorella Maicol Ciani Michael Rogenmoser Chaoqun Liang Angelo Garofalo Francesco Conti 🇮🇹🇪🇺

We present "A Flexible Template for Edge Generative AI with High-Accuracy Accelerated Softmax & GELU" based on a 8-core RISC-V cluster with a 24 × 8-PEs tensor processing unit and a novel accelerator for BFloat16 softmax. See arxiv.org/pdf/2412.06321 Yvan Tortorella Angelo Garofalo

Just before the end of the year, here is our paper "Open-Source Heterogeneous SoCs for AI: The PULP Platform Experience" with focus on designing heterogeneous AI acceleration SoCs. Find it here: arxiv.org/pdf/2412.20391 Francesco Conti 🇮🇹🇪🇺 Angelo Garofalo Davide Rossi Giuseppe Tagliavini

We present a lightweight, modular, technology-independent & open-source real-time extension to AXI4 interconnect. See "AXI-REALM: Safe, Modular and Lightweight Traffic Monitoring and Regulation for Heterogeneous Mixed-Criticality Systems" arxiv.org/pdf/2501.10161 Thomas Benz

Next for #DATE2025 in Lyon, Chaoqun Liang will present a versatile Transaction Monitoring Unit for AXI4-based SoCs. Find the paper on arXiv under "Towards Reliable Systems: A Scalable Approach to AXI4 Transaction Monitoring" arxiv.org/pdf/2501.17605 Thomas Benz Alessandro Ottaviano

Addressing the softmax bottleneck in PULP Platform clusters, at a minimum hardware cost. This is critical for efficient attention computation, especially when GEMM/V is accelerated by the redmule tensor engine!

The poster and slides from Chaoqun's Chaoqun Liang #DATE2025 contribution "Towards Reliable Systems: A Scalable Approach to AXI4 Transaction Monitoring" are now online. Check them out: pulp-platform.org/docs/date2025/… & pulp-platform.org/docs/date2025/…