alhambrabits

@alhambra_bits

AlhambraBits is the entry to a new learning concept for Digital Electronics. Our goal is to teach solving problems by applying the logic behind the hardware

ID: 901332564647919616

http://www.alhambrabits.com 26-08-2017 06:36:44

658 Tweet

786 Takipçi

13 Takip Edilen

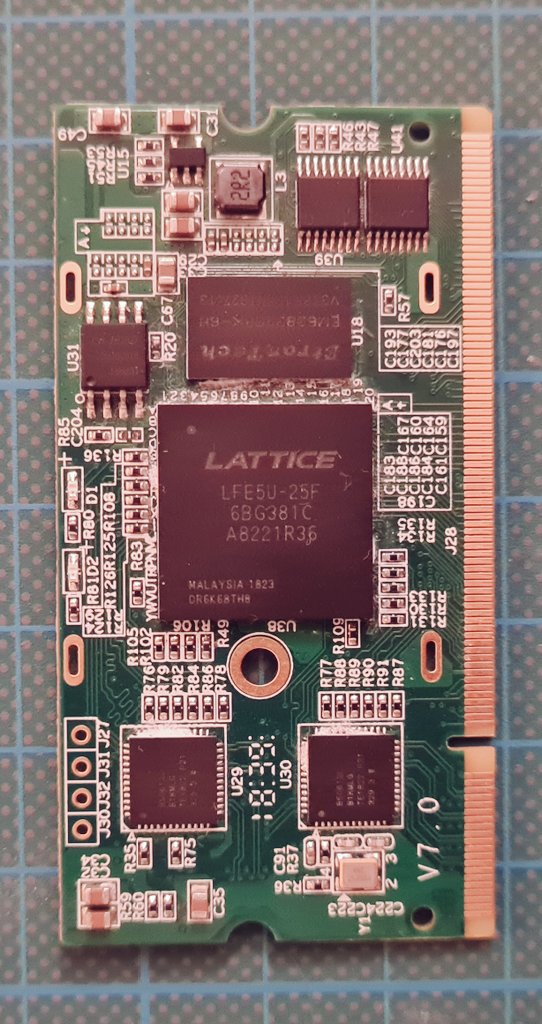

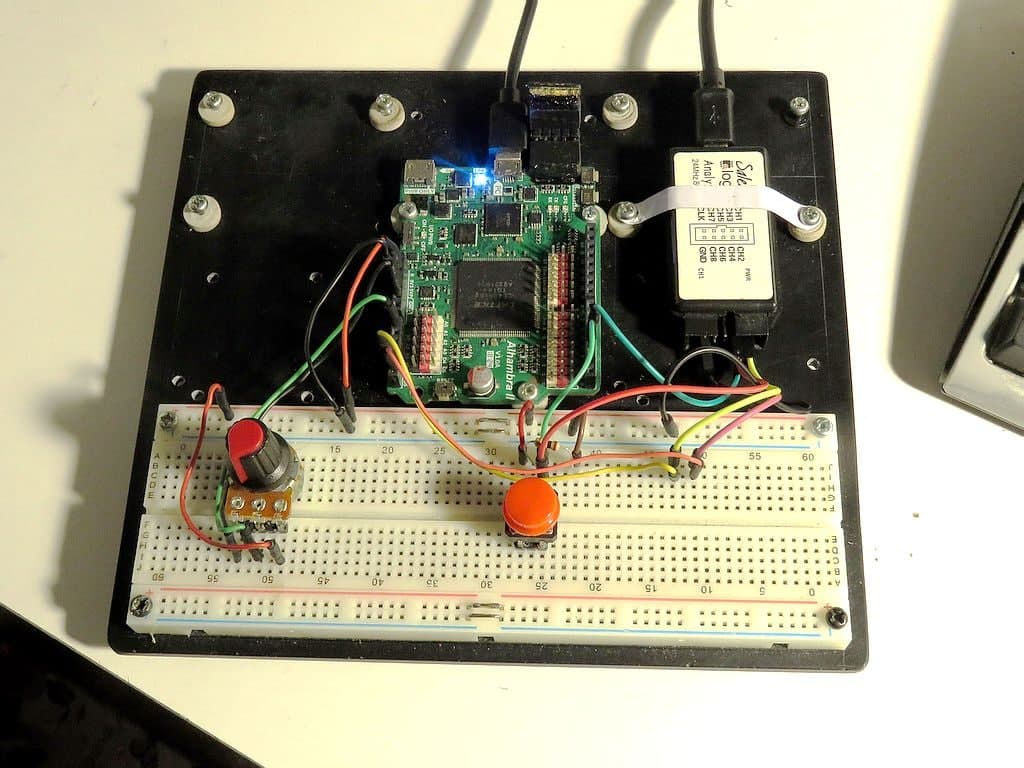

Juan Gonzalez @ETSIT_URJC Grado en Ingeniería de Robótica Software @ URJC en la Politècnica UdL también tenemos uno muy parecido (y también controlado con la Icezum Alhambra II de alhambrabits) #FPGAWars #Icestudio

mrdoornbos Renegrade ln2718 Bought mine from here, the official store alhambrabits.com/buy/ alhambrabits

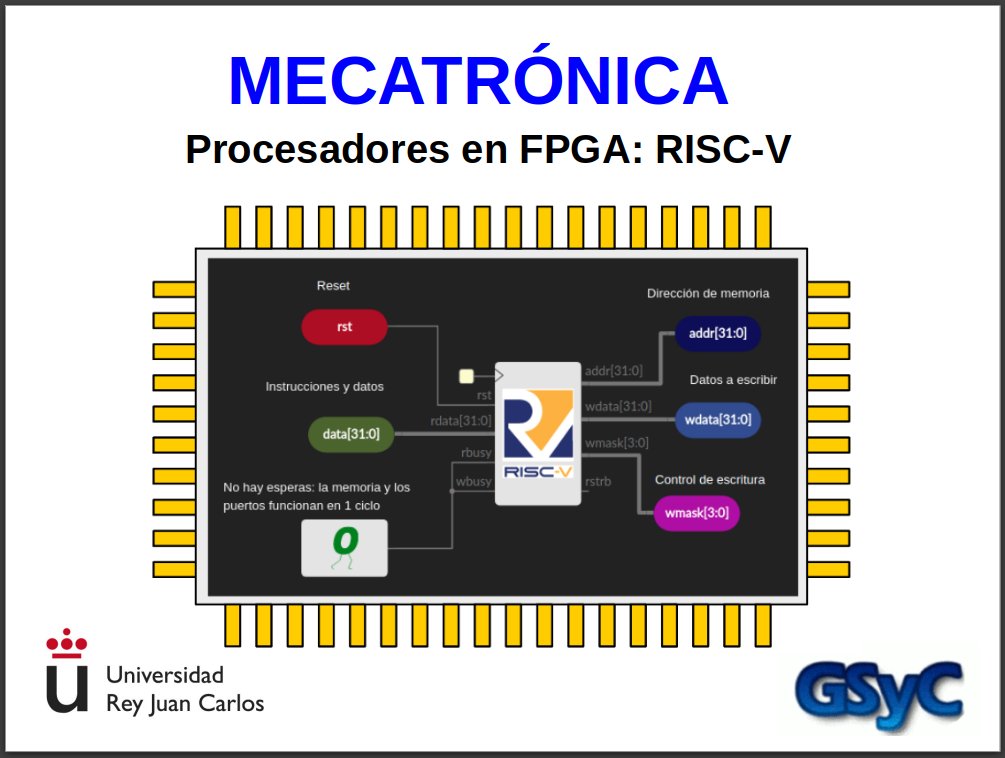

ChuxMan Skynetwalker 🛠 Ese es el Riscv que hemos usado en la asignatura de Mecatrónica Grado en Ingeniería en Robótica Software @ URJC , pero desde #Icestudio Es super compacto y buenísimo. Bruno Levy es un crack! 😀 Sesión 7: Procesadores en FPGA: RISCV github.com/myTeachingURJC…

Alejito (don pichurria) Rinconcibiris® El clásico: The Designer's Guide to VHDL : Peter Ashenden

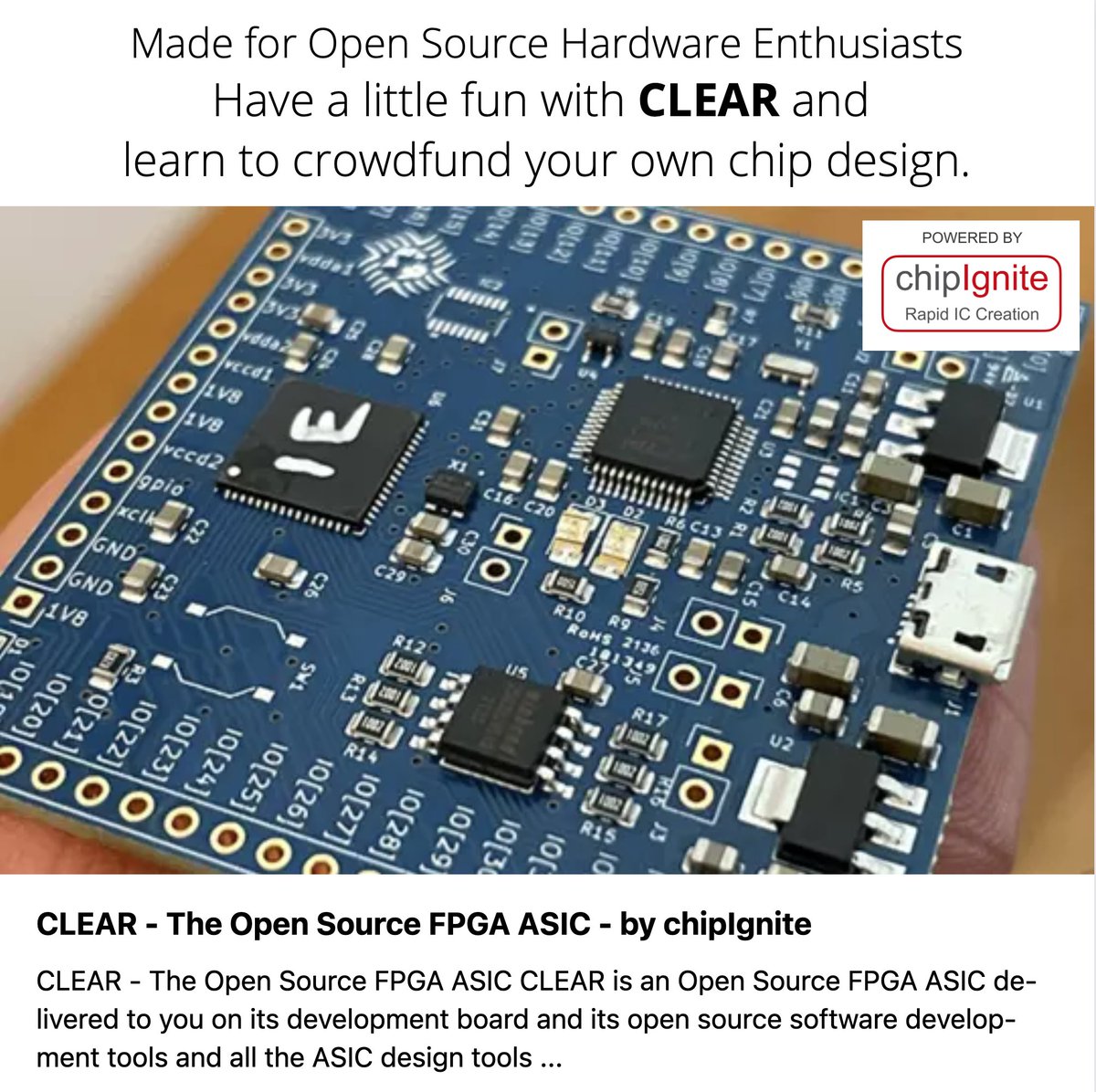

CLEAR - The Open Source FPGA ASIC lnkd.in/eYwN4wR5 efabless.com SkyWater Technology Foundry #opensource #asic #fpga #efpga #efabless #skywater #chipignite #groupgets #crowdfunding